Give your designers a seamless, efficient path from design capture through verification. Tanner EDA tools for analog and mixed-signal IC design enable faster time to market, lower costs, fewer risks, and shorter design cycles. You can implement a complete, integrated design flow with Tanner EDA's HiPer Silicon.

Designing Half Adder using S Edit by Tanner Tools Safi Ahmed. How to install Tanner EDA Tools v13.0 on Windows 7/8. How to include Library files and Model files into Tanner EDA - Duration: 7. Tanner Tools V15 Free Download With 19 DOWNLOAD. S-Edit 13 User Guide—Contents (Continued) S-Edit 13 User Guide 2 Setup Technology Protection.

HiPer Silicon is a complete IC design suite that encompasses schematic capture, circuit simulation, waveform probing, physical layout, foundry-compatible DRC, and verification. It can increase your productivity and speed your design from concept to silicon. HiPer Silicon includes S-Edit, T-Spice, L-Edit, and HiPer Verify. Each tool has been significantly enhanced in the past year.

S-Edit

S-Edit enables schematic capture for the most complex full custom IC design. This easy-to-use Windows®-based design environment for schematic capture integrates tightly with Tanner EDA's simulation, physical layout, and verification tools.

New features in S-Edit include:

Hierarchical Find

Search for nets, instances, and objects through the hierarchy with filtering and optionally replace or modify them.

Design Navigator

Efficiently traverse design hierarchy with top-down and bottom-up hierarchical view.

Drag and drop instances directly from the library browser to speed through your design.

Verilog Import

Structural Verilog can be imported into S-Edit as a netlist.

T-Spice

T-Spice lets engineers simulate key blocks during the design process. It puts you in control of simulation jobs with an easy-to-use graphical interface and a faster, more intuitive design environment. T-Spice delivers highly accurate results by supporting the latest foundry, transistor, and behavioral models, with its new multithreading capability for faster runtimes, you will speed your design from concept to silicon faster than ever.

T-Spice includes the following new features:

Verilog-A Support

The Verilog-A feature of T-Spice allows designers to describe and simulate analog circuits behaviorally. For analog designers, Verilog-A enables a top-down approach to circuit design, and allows co-simulation between behavioral blocks and device level analog SPICE netlists. For process developers especially TFT and MEMS process, Verilog-A provides an efficient language for describing device behavior, which is portable across simulators.

T-Spice is compliant with all Verilog-A specifications in the latest standard Verilog-AMS LRM (Language Reference Manual) version 2.2, passes the Compact Model Council test suite, and is fully compatible with Spectre®, H-Spice®, and SmartSpice®.

User Interface Improvements

Simulations now operate on the active Spice file. Filenames of output files are auto-generated from the input filename, and can be optionally placed in a new folder with a time stamped name each time the simulation is run. This allows input files or result files to be easily compared in W-Edit or a 3rd party differencing program.

L-Edit

L-Edit enables analog/mixed-signal designers to automate the layout of similar circuits for different ICs. It meets your needs by combining the fastest rendering available with powerful features. You can get started with minimal training, and draw and edit quickly with fewer keystrokes and mouse clicks than in other layout tools.

Enhanced XrefCells

X-Ref cells, or externally referenced cells, now point directly to the final target cell in a chain of references. This eliminates the need for multiple copies of X-Ref cells that can occur when libraries with multiple reference levels are used.

SDL Enhancements

Flylines are automatically updated when moving instances.

Pins in the SDL Navigator can be viewed by net or by instance.

Existing geometry and geometry that has been added manually can be marked as part of a specific net allowing selection and rip-up of geometry by net.

Structural Verilog can be imported into SDL as a netlist.

Enhanced CurveTools

Wires can have fillets added that retain equal width.

Fillets can be added to curved objects such as a torus and multiple edges are considered as a single edge when adding a fillet/chamfer for curved objects that have been converted to all-angle objects.

Tanner Eda Tools V13.0 Free Download

Extract StandardStarting in v13.1, Extract Standard will be much faster but it will still only produce flat netlists. Also, the block (sub-circuit) extract feature of Extract Standard will be discontinued in v13.1 because HiPer Verify now has true hierarchical netlist extraction.

HiPer Verify

HiPer Verify runs Calibre® and Dracula® rule sets hierarchically and natively, and it tightly integrates into the L-Edit environment, allowing design rule violations to be identified and repaired early before they become a major problem.

All-angle hierarchical Calibre compatible netlist extraction

HiPer Verify can extract a hierarchical spice netlist from layout using a Calibre format command file, with performance significantly faster than Tanner Extract Standard. HiPer Verify provides default property computations for built-in devices or user code may be written to compute custom properties from a set of pin and auxiliary layers. User-defined devices (sub-circuits) may also be specified.

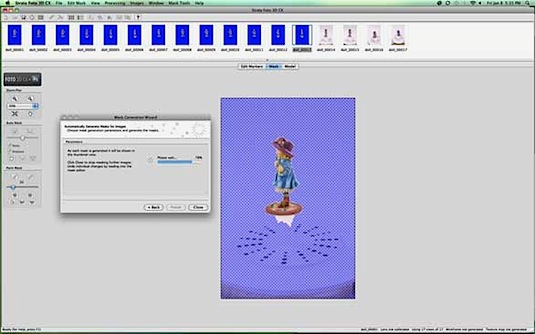

HiPer PX

HiPer PX is a 3D physics-based parasitic extraction tool that extracts devices and creates compact and accurate RC models for interconnects up to a user-defined signal frequency. HiPer PX uses a fast and comprehensive interpolation method or an efficient boundary-element method for capacitance extraction and an efficient finite-element method to accurately extract interconnect resistances.

Tanner Eda Tools V13.0 Download Free

HiPer PX

Extracts 2D interconnect resistance and capacitance for fast extraction times and 3D RC for more accurate parasitic extraction.

Output is a simulation-ready SPICE netlist of devices and RC parasitics.

Supports reduction of RC networks based on a user-specified time constant.

On-Demand Training Libraries

Tanner EDA On-Demand Training Library

Learn the basic functionality of Tanner S-Edit for schematic entry, Tanner L-Edit for layout, and how it can be employed to draw MEMS layout.

Tanner EDA L-Edit MEMS: Basic MEMS Layout On-Demand Training Course

Learn how to utilize the power of L-Edit to create, verify and stream in/out MEMS layout efficiently in the shortest time possible.

Tanner Analog IC Design: L-Edit Basic On-Demand Training Course

This training helps you gain knowledge of basic operations of L-Edit IC to perform physical designs of integrated circuits.

Tanner Analog: Layout-Advanced On-Demand Training Course

This learning path helps you gain knowledge of advanced operations of L-Edit IC like SDL and Node Highlighting. You will also learn how to use Calibre One for Physical…

Explore Siemens Analog/Mixed Signal Custom Design Flow

Explore Siemens custom analog IC design flow to increase productivity from design capture, simulation, physical layout, and verification to tape-out.

To…

Live Online Training

Tanner Analog IC Design: Full Flow

Tanner Analog IC Design: L-Edit Basic

Live online

Live onlineTanner EDA L-Edit MEMS: Basic MEMS Layout

In this introductory course, you'll learn the basic functionality of L-Edit, and how it can be employed to draw MEMS layout. The course includes concept presentations,…

Available By Request

These classes can be scheduled at your convenience, upon request, at a Siemens EDA training center or your company site. We can also customize a course to fit your needs.